移相全桥作为类BUCK拓扑,其原边能实现ZVS,副边易于实现大电流输出,对输出电容要求低。使用占空比调制更容易实现宽的输入输出范围,在工业界已经有大批量应用。此篇文章的内容是描述在PLECS仿真软件中如何实现移相全桥的仿真模型,这种PWM实现方法也十分易于在其它仿真环境和DSP中实现。

第一部分移相全桥简介

硬件框架:在原边增加了一个谐振电感,用于实现原边的ZVS用,其他和普通全桥一致。

控制波形:

驱动AB为超前桥臂驱动信号,驱动CD为滞后桥臂驱动信号。通过调整CD滞后于AB的时间来调整传递到副边电感上的方波占空比。

第二部分移相驱动波形的实现

不同于模拟控制器UCC3895这种通过大量锁存器实现的方法,在数字控制器和仿真环境中用三角波载波的方法更容易实现移相驱动波形。

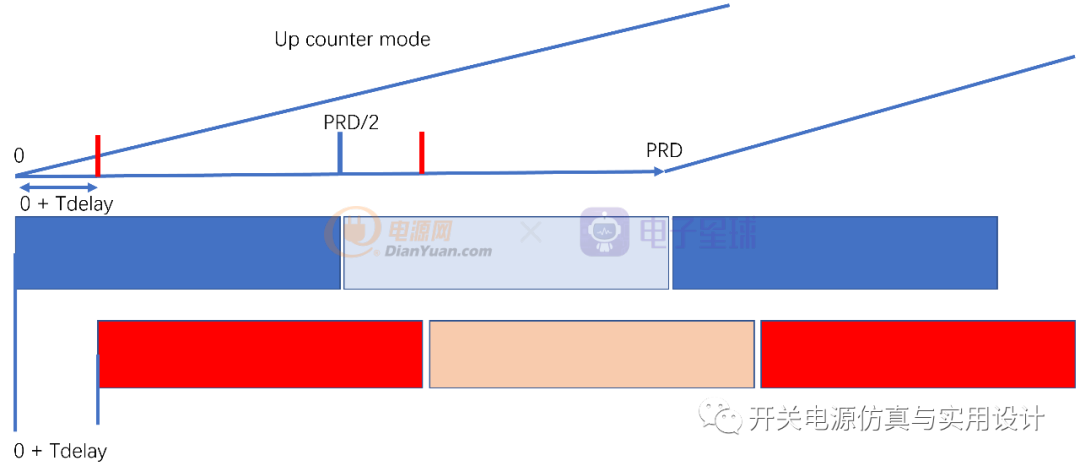

可见下图示意,把超前桥的高端驱动放在三角波的是0~0.5*prd产生,低端波形加入死区后互补产生。滞后桥臂的高端驱动根据所需要的滞后时间在三角波的(0+Tdelay)~(0.5*prd+Tdelay)产生,低端驱动加入死区时间后互补输出,这样就很容易的得到了移相全桥控制所需的超前和滞后PWM波,控制器通过调整Tdelay的大小,也就实现了滞后桥滞后角度的调整。

在PLECS仿真环境里的实现:

用单上升沿的三角波输入,当三角波大于设定的原点作为桥臂的PWM起点,同理PWM的结束点就用三角波小于(起点+半周期)这个点,有了两个时间点就可以用and逻辑把高端驱动捕获,再通过加入死区时间得到互补的高低端驱动,可见下图:

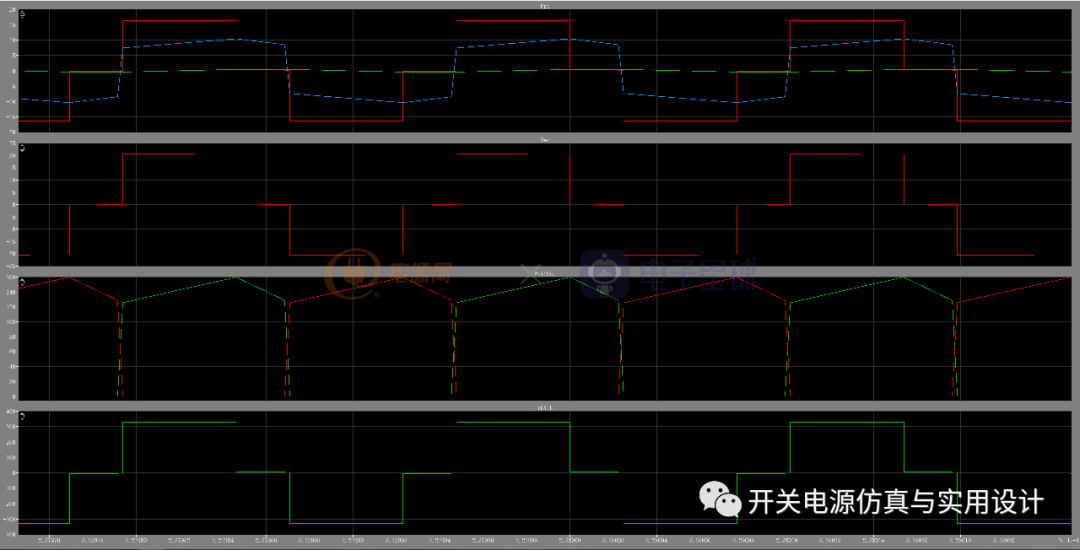

PWM发生器得到波形为可见下图,其中中间为超前桥驱动,从三角波的零点开始到中点关闭。滞后桥的起点是三角波的零点加控制值,然后关断点是三角波的中点加控制值。

闭环控制:

通过增加闭环控制器就可以很容易实现闭环,闭环这一块可以用PID或其它控制器实现,下图是电压模式控制的实现:

启动波形:

说明:关于环路设计部分后面会单独写一篇。感谢观看,谢谢。

参考文档:

1,Phase-ShiftedFull-Bridge,Zero-Voltage

TransitionDesignConsiderationsApplicationReport

LiteratureNumber:SLUA107ASeptember1999–RevisedAugust2011

2,UCC3895数据手册。

3,脉宽调制DC/DC全桥变换器的软开关技术(第二版)阮新波著

电压模式控制的移相全桥变换器,在闭环控制的角度上可以看成是BUCK类的衍生。毕竟不管移相全桥,硬开关全桥,双管正激,都是通过控制原边开关的占空比,再通过隔离变压器降压,变成输入为Vin/N的方波加到次级的BUCK电路上。所以下文将从隔离BUCK的角度来做闭环控制器的参数设计。

下图是把实际电路简化为环路控制的视角:

PWM增益用于描述占空比为1时所对应的PWM斜坡高度,可以当作PWM发生器的精确度来理解。数字系统使用与模拟一样的办法,比如模拟控制IC中斜坡高度电压为5V,那么三角波的增益为1/5=0.2。而在数字控制器中,使用upcounter模式时,此处的增益就是1/tbprd。

有了上文的功率级传递函数,PWM的增益,在结合拓扑的实际参数就可以开始环路设计了,下面是功率级的参数信息:

Vin:300~400V

Vo:12V

Io=160A

Np/Ns=22/1/1

Lf=1uH

Lr=5uH

Cout=1000uF

Resr=5mohm

原理图可见:

稳态工作波形:

有了功率功率级参数和控制到输出的传递函数,就可以在matlab里面开始环路设计了。第一步先求出控制到输出的传递函数,再然后使用matlabsisotool工具直接设计闭环控制器的参数,即可简单快速的完成设计。附录中是详细代码,下文将一步一步的展示具体过程:

第一步是计算控制到输出的传递函数,下图是控制到输出电压的传递函数Bode,在LC谐振频率处存在很明显的增益尖峰,因此可以把穿越频率放在700~1000Hz处。对了你可能会问,为什么低频增益这么低,是因为被Gpwm拉低的,后面在补偿器里面可以补偿起来。备注:控制到输出的传递函数离散的方法看参加这篇文章:《理解数字控制系统的环路设计-入门级》。

传递函数:

Gvd=0.0007013z^2+0.001605^(-2)*--------------------------------------z^2-1.59z+0.7727Sampletime:1.5e-05secondsDiscrete-timetransferfunction.

bode图:

第二步调用SISO工具开始环路设计。

补偿器的传递函数为:

此时matlab输出的补偿器输传递函数在w域,可以使用C2D工具离散到Z域,就可以在Z域计算系统的开环增益和分析稳定性。计算得到补偿器的Z域传递函数为:

Gc_z_v=

8.427z^2-10.16z+2.118

---------------------------

z^2-1.924z+0.9241

Sampletime:1.5e-05seconds

Discrete-timetransferfunction.

第三步检查开环增益的稳定性:根据控制到输出和补偿器的传递函数就能得到环路增益Bode,可见下图。此时系统是稳定的,到此环路设计完成,如果参数不满意,可以根据上诉过程继续优化。

备注:环路仿真部分,后面再单独发来一篇。感谢观看,谢谢。

致谢:感谢时光如水指正昨天文章中超前桥错误的问题,谢谢。

附录matlab代码:

%Phaseshiftfullbridgedcdc%Vin300-400%Vo12V/160A%By:Yangshuai%2020/03/06clearall;echooffclc%Vin=300~400VVO=12VIo=160A%Lf=1uHCo=1000uFesr=5mohm%Np/Ns=22/1/1%Fsw=66.6KHz%ConverterinfoVo_min=300;vo_max=400;vo=12;Io=160;RL=vo/Io;G_vout=RL;np=22/1;pwm_count=1500;%PWMcountergf_pwm=1/pwm_count;%GpwmTs=15e-6;%controlerTsTd=1.5*Ts;%controlerTdelay%PowerinfoL=1e-6;%buckLfC=1000e-6;%buckCoutRc=5e-3;%buckCoutesrfo=1/(2*pi*sqrt(L*C));%DutycontroltoVoutTF:num_Gps=gf_pwm*(vo_max/np)*[Rc*C1];denom_Gps=[L*C*(1+Rc/RL)(L/RL+Rc*C)1];%BuildVloopTfGps_dly=tf(num_Gps,denom_Gps,'inputdelay',Td);%s-domainplantwithcomputationdelayTd%Gvd=c2d(Gps_dly,Ts,'zoh')%DiscreteplantwithZOH,KdandTd%%DutycontroltoIoutTF:Gif=Gvd*(1/RL);zpk(Gif);%PlotGplbodeGpl=0;GTLP=1;call_siso=1;ifGplx=bodeplot(Gvd,Gif);setoptions(x,'FreqUnits','Hz','PhaseVisible','on')gridon;ifcall_siso%CallcontroltoolcontrolSystemDesigner(Gvd)ifGTLP%VoltageloopcompFC=514HZnum_c=3.4186e5*conv([0.000231],[1.3e-51]);den_c=[0.0001910];Gc_w=tf(num_c,den_c)Gc_z_v=c2d(Gc_w,Ts,'tustin')%IloopCOMPGc_z_i=Gc_z_v*(vo/Io)%openloopbodeTvloop=Gvd*Gc_z_v;Tiloop=Gif*Gc_z_i;z=bodeplot(Tvloop,Gvd,Gc_z_v);setoptions(z,'FreqUnits','Hz','PhaseVisible','on');gridon;VMC移相全桥的环路仿真与应用第三节

第一步利用黑盒思想在仿真软件中扫描功率级传递函数

比如一个拓扑,它的控制变量是频率,在某个我们设定的稳态工作点的工作频率是75KHz。我们可以在仿真软件里面设定扰动变量叠加在75KHz的稳态常量上。然后不管变频驱动的产生原理,不管开关管,电感,变压器,电容等器件的具体存在,而是把PWM发生器和功率级当作一个黑匣子,可见下图示意。我们只关心黑匣子的输入和输出结果,通过仿真软件的数据处理,把黑匣子的输入和输出整理成Bode图输出。就是利用仿真软件扫描环路的核心观点,当然你要求细化分析也可以,在一些文献中VCO的增益也需要独立建模出来,这里只是为了简化,就打包在一起分析了。

根据上面的思想,我也可以把移动相全桥的PWM部分和功率级当成一个黑匣子,移相角度控制变量设定为0~1.0,在控制变量为1时移相角度为最大值。只需找到我们关心的功率级的稳态工作点,利用黑匣子的办法即可扫描得到控制变量到输出信号的Bode图。下图是在Simlpis环境中建立的移相全桥PWM和功率级部分,稳态工作点为移相角度95%,扰动变量叠加在移相调节部分,输出信号取全桥的输出电压,可见黄色星形标注。

扫描得到相位调整到输出电压的波形可见:

移相驱动波形:

第二步根据Bode图数据得到控制到输出传递函数

我常用的两个仿真软件(Plecs和Simlpis)都能将Bode图波形数据导出为ACSLL文件。下图是Simlpis的操作方法,Plecs环境以前有写过,这里不再累述。

点复制数据。

到Ecxel文件里面粘贴数据,然后转为角频率和幅度,准备导入到Maltab。

导入成功后:

打开systemIdentification工具,导入freqdomaindata,选择Amp/phase,连续域把采样时间设0。

对于简单的模型,使用3P2Z拟合就能得到非常好的效果,下图是接近程度为99.8%的传递函数,到此我们已经得到了想要的东西。

第三步使用SISO工具自动设置控制器参数

具体实现可以参考以前发过的:《利用maltab的systemidentification获取系统的传递函数加速你的环路设计》。

在上文得到的s域传递函数:

Gvd=

5.221e04s^2+4.151e10s+6.062e15

------------------------------------------

s^3+5.051e05s^2+1.062e10s+4.672e14

使用采样到PWM更新延迟1.5控制周期将S域传递函数离散到Z域,如果你是模拟控制就无需这一步操作。备注:控制到输出的传递函数离散的方法可参考这篇文章:《理解数字控制系统的环路设计-入门级》。

然后调用siso工具,选择合适的带宽和相位余量后,就结束了设计。下图是一组闭环控制参数,开环增益Bode和根轨迹显示都是处于稳定区域。各位可以自行把玩一番,加深了解。

更多精彩内容,尽在电子星球APP()

七篇储能技术文章,让你进阶新高度

六篇技术文章,让你秒懂电容的脾气秉性

储能,新能源的后浪已至

五篇文章帮你开启DSP的学习思路

汇总篇:关于PID知识,重点在此

-

“能一次看到这么多高科技产品,真是大饱眼福!”

2025-08-31 -

800V电驱动系统详细解析(第二期)

2024-11-19 -

友善电子推出双 2.5G 迷你开发板 NanoPi R5C,售价 349 元起

2025-04-19 -

PCB抄板过程曝光

2024-11-16