简单地说,逻辑门是数字电路的基本结构,所有数字电路都由与门和、与非门、或非和反相器组成。逻辑门电路常用于各种电子设备硬件,如计算机、数字手表、电视、手机…

1,非门,又称反相器,简称非门,是逻辑电路的基本单元。非门有一个输入和一个输出端。当其输入端为高电平(逻辑1)时输出端为低电平(逻辑0),当其输入端为低电平时输出端为高电平。也就是说,输入端和输出端的电平状态总是反相的。非门的逻辑功能相当于逻辑代数中的非,电路功能相当于反相,这种运算亦称非运算。

非门符号

非门真值表

非门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityNOT_GATEis

Port(A:inSTD_LOGIC;

B:outSTD_LOGIC);

NOT_GATE;

architectureBehavioralofNOT_GATEis

begin

B=NOTA;

Behavioral;

仿真波形

非门仿真波形

2,与门是执行“与”运算的基本逻辑门电路。有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

与门符号

与门真值表

与门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityAND_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

AND_GATE;

architectureBehavioralofAND_GATEis

begin

C=AANDB;

Behavioral;

仿真波形图

与门仿真波形图

3,与非门是数字电路的一种基本逻辑电路。若当输入均为高电平,则输出为低电平;若输入中至少有一个为低电平,则输出为高电平。与非门是与门和非门的叠加。

与非门符号

与非门真值表

与非门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityNAND_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

NAND_GATE;

architectureBehavioralofNAND_GATEis

begin

C=ANANDB;

Behavioral;

与非门仿真波形图

4,或门又称或电路、逻辑和电路。或门有多个输入端,一个输出端,只要输入中有一个为高电平时(逻辑“1”),输出就为高电平(逻辑“1”);只有当所有的输入全为低电平(逻辑“0”)时,输出才为低电平(逻辑“0”)。

或门符号

或门真值表

或门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityOR_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

OR_GATE;

architectureBehavioralofOR_GATEis

begin

C=AORB;

Behavioral;

或门仿真波形图

或门仿真波形图

5,或非门是数字逻辑电路中的基本元件,实现逻辑或非功能。有多个输入端,一个输出端,多输入或非门可由2输入或非门和反相器构成。只有当两个输入A和B为低电平时输出为高电平。

或非门符号

或非门真值表

或非门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityNOR_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

NOR_GATE;

architectureBehavioralofNOR_GATEis

begin

C=ANORB;

Behavioral;

或非门仿真波形图

或非门仿真波形图

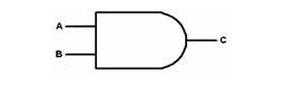

6,异或门是数字逻辑中实现逻辑异或的逻辑门。有多个输入端、1个输出端。若两个输入的电平相异,则输出为高电平1;若两个输入的电平相同,则输出为低电平0。亦即,如果两个输入不同,则异或门输出高电平。

异或门符号

异或门真值表

异或门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityXOR_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

XOR_GATE;

architectureBehavioralofXOR_GATEis

begin

C=AXORB;

Behavioral;

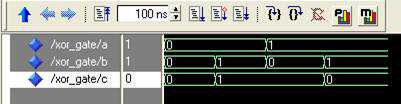

异或门仿真波形图

异或门仿真波形图

7,同或门也称为异或非门,是数字逻辑电路的基本单元,有2个输入端、1个输出端。当2个输入端中有且只有一个是低电平时,输出为低电平。亦即当输入电平相同时,输出为高电平。

同或门符号

同或门真值表

同或门真值表

VHDL代码

libraryIEEE;

_LOGIC_1164.ALL;

entityXNOR_GATEis

Port(A:inSTD_LOGIC;

B:inSTD_LOGIC;

C:outSTD_LOGIC);

XNOR_GATE;

architectureBehavioralofXNOR_GATEis

begin

C=AXNORB;

Behavioral;

同或门仿真波形图

同或门仿真波形图

-

医药行业专题报告:NK细胞为免疫系统先锋队,关注其细胞免疫疗法

2025-04-20 -

延华智能——智慧的轨迹:从上海延华到智能科技巨头

2025-09-23 -

好利科技上涨5.16%,报11.41元/股

2025-07-19 -

大指挥官2.0T引擎深度拆解:黑科技十足,赢得40万国产车主的点赞

2025-12-09