电沉积(简称ED)是一种将金属离子以电化学方式沉积在电极表面的金属电镀方法,广泛应用于电子、微电子、光电子、纳米科技和材料科学等领域。

它可以实现对金属的精确控制和定向沉积,制备出具有特定形状、尺寸和性能的金属薄膜、电极和纳米结构。

然而,开发ED(电沉积)工艺本身是一项复杂的任务,在此过程中,需要考虑与现有的硅基技术的兼容性。

虽然ED工艺通常允许低温、低电位和相对简单的电解质,但使用导电基底限制了其适用性,为了使ED技术在微电子应用中发挥作用,通常需要对表面进行改性处理。

由于这个过程涉及复杂的热力学和动力学问题,直接在半导体上进行金属沉积并不容易,此外,沉积金属原子和硅表面之间的相互作用能较低,也会对沉积产生影响,通过选择适当的ED条件以及避免强氧化环境,可以调节这些相互作用。

ED(电沉积)过程通常遵循Volmer-Weber生长机制,这导致沉积速率缓慢、形态差异大以及结晶度较低等问题,因此,为了改善质量,需要进一步处理非晶/纳米晶电沉积材料。

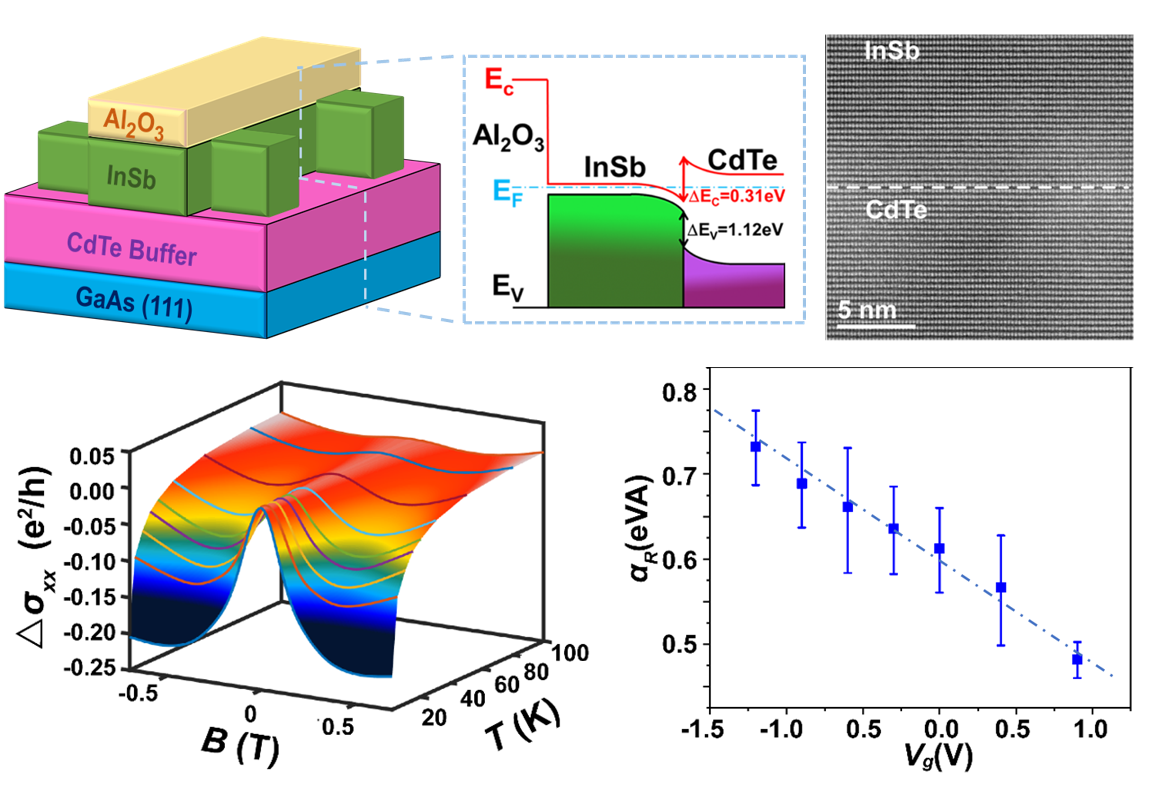

对于金、铜和铂在硅上的沉积机理,已经有详细的研究结果可供参考,例如直接电沉积金、氧化铜、氧化锌、甘以及最近的InSb方法,仍存在一些限制因素,如粘附力不足、与其他元素的相容性差以及非故意杂质等。

为了解决这些挑战,必须仔细选择合适的电沉积工艺,并优化电解质的组成,同时准备足够数量和高质量的基底。

在半导体工业中,硅上电沉积铟和铟基半导体具有潜力,然而,这些沉积物中含有大量的钠、硫、氯和碳等杂质,直接在硅上脉冲电合成InSb的方法已被开发出来,并且观察到类似的大量碳和氧杂质存在。

改进方法包括通过在Mo箔上电沉积或蒸发In来制造太阳能电池所需的高纯度InP同时,采用薄膜磷化技术以及电子束蒸发铟,在Si/SiO2底片上成功制备了大尺寸(100μm)高迁移率晶态InAs和InP材料[2/哞x底物]。

该方法已经得到进一步改进并应用于制备光电级别别的InP和InAs材料在硅衬底上进行外延生长时,由于液相模板受限几何稳定性限制,在狭窄设计窗口内操作,并且未实现晶体与衬底之间完美匹配关系。

湿法技术,如电沉积和汽相生长,具有快速、均匀的模板填充特性,同时,湿法技术还能够迅速填充各种形状的复杂纳米或微米级模板,为饱和V元素提供理想的平台。

使用3D氧化物模板不仅可以控制In的电沉积形状,还能在ED和饱和步骤之间保护其不被表面氧化,铟从模板内的小工作电极开始进行电沉积,然后将模板放置在MOCVD室中。

在适当的V元素气氛下使液体饱和,从而合成III-V族半导体,在这一步骤中,之前的工作电极现在充当了熔融结晶的成核区域,这种方法能够有效利用湿法技术的优势,实现模板填充和半导体材料合成的一体化过程。

氧化硅中铟的电沉积xSi上的模板选择铟作为电沉积材料,与V族元素(P、As、Sb)一起加工以形成各种III-V族半导体,与Au或Cu不同的是,In在与Si接触时不会产生有害的污染物,杂质对结晶过程有害,阻碍单晶材料的形成。

为了抑制电解液中污染物进入In沉积物,采用了简单而有效的方法——只使用双组分镀液:InCl3在去离子水中预期还原反应生成3+离子,在电解质分解的情况下唯一副产物是气体(Cl2和H2),可通过Ar鼓泡从溶液中提取,选择合适的电化学技术可以调整沉积物成分和形态。

更复杂的电位-电流波形或多步方法通常需要更复杂的电解质,使用双极计时法控制持续时间来调节体积,并将小种子孔嵌入模板作为工作电极进行填充,掺磷硅片具有各种十字和直线设计模板。

在交叉设计中填充非均匀性可能由于凹角结构引起,该方法能够实现芯片上均匀填充并得到高品质半导体沉积物,并且比共形填充非晶和纳米晶InSb沉积物表现出更好的规则性。

由铟制成的独立结构在高达其熔化温度的情况下表现出稳定性,该温度为157℃。当超过此温度时,熔体的高表面张力会导致形成球形熔体,例如液滴,相反地,在模板的机械和三维限制下,In结构应该能够进行高温处理。

为了验证填充进一氧化硅模板之外部分的机械稳定性,在560℃下以H环境中对具有相同Tm值的器件样品进行30分钟退火。

尽管Si/SiO2之间存在较大膨胀差异,但在退火过程中仍然存在着x和In熔体,并且这可能是开放模板结构允许熔体松弛的结果,没有检测到In通过模板壁发生可见扩散或泄漏。

在退火后,可以明显看到入口孔附近In系统损失的情况,这归因于铟向外扩散通过入口孔发生了,在退火和凝固后,填充进去的In显示出稍微更均匀分布,在拐角结构中一些凹陷区域在固化后仍未完全被填充。

退火样品的结构和成分经过(S)TEM-EDX进行了分析,呈现出几个器件横截面的低分辨率概览,包括具有In-Si界面的种子孔,模板在结构上保存完好,没有裂缝,并保持均匀填充,其中一个结构的高倍放大图像显示。

在底角处具有高表面曲率的区域有时未被完全填充,导致局部空隙,样品元素分析通过相应的TEM-EDX进行,其中红色、蓝色和绿色区域分别对应于铟、氧和硅,再次清晰地显示出空隙可能源自制造残留物或FIB样品制备。

结果表明,溶液ED工艺产生高纯度的结晶铟沉积物,将ED工艺应用于模板中的选择性生长允许制造由铟制成的轮廓分明的亚微米结构,在模板中使用小的嵌入式工作电极导致了大部分与Si衬底隔离的结构,因此理想地适合于器件制造。

模板中金属到半导体的转换通过在硅上制造In合金或In-v族半导体,填充微结构的三维约束、高纯度和热稳定性可以作为起点。

在所有可用的选择中,重点是半导体,并且选择砷来饱和电镀沉积的铟,以便从Si种子晶体中生长出InAs。

将填充有电镀In的模板装入MOCVD反应器中,在远高于TBAs分解温度加热后使As扩散到受限界面并形成外延生长的InAs晶体核心,只要a供应持续不断,该晶体最终会膨胀并消耗掉所有的In,在去除二氧化硅后使用x模板更好地展示了最终的InAs器件。

尽管较大沉积物可能会延伸到十字架末端之外,但通常情况下,在8个凹边结构中观察到这种现象时很正常,因为初始填充结构与其相比存在一些缺失边缘。

对于评价样品结构进行横截面样品和TEM切片(S)TEM分析非常必要,低分辨率横截面图显示inas(假红色)被两端有入口孔的模板包围,而种子孔位于设备中心.在几个样品中观察到特定对比表明存在晶体结构和平面缺陷,同时也观察到与ina一起空洞存在。

InAs器件的TEM横截面位置略微偏离中心,超出了种子孔的位置,并且与之前的样品相似,在低分辨率图像中,可以看到样品表面存在平面缺陷,下方的高分辨率图像显示了相应的点阵图像和沿设备长度方向的快速傅立叶变换(FFT)。

晶格信息表明,样品大部分是单晶InAs,存在平面缺陷,而最右侧的部分则由纳米尺寸的InAs晶体组成,实验中使用的快速傅立叶变换与模拟结果的比较证实了样品中InAs晶体的取向,并且与Si(001)衬底没有外延关系。

在样品中,InAs晶体首先出现在两个入口孔处,随后是In和InAs的间隙和片段,In和InAs之间有很好的相分离。

籽晶区域仍然被In填充,并与Si衬底接触,这种不均匀的加工结果可能是由于熔体中或模板表面上InAs晶体多次随机成核事件的结果。

一旦膨胀的InAs晶体堵塞了部分填充In的通道,As供应就停止,导致InAs-In固态熔体的相分离,尽管观察到了空隙的存在,但没有检测到通过模板壁的渗漏。

低温工艺将样品装载到MOCVD反应器中,并加热到超过TMSb的裂解温度,设定合适的Sb通量和处理持续时间,以将In填充的通道转化为InSb,产生均匀对比度的结构。

通过SEM检查来评估结果,根据In-Sb相图,过短或过长的暴露时间会导致剩余的金属In(Sb)沉积物,在SEM中可以观察到亮度对比区域,类似于As扩散实验,观察到具有不均匀对比度的Sb扩散结构,不均匀的晶体结构归因于熔体中或模板表面上InSb晶体的随机成核事件。

为了评估低温InSb的晶体结构,制备横截面样品和TEM薄片,并进行(S)TEM分析,通过显示低温InSb样品的横截面图像和从标有箭头的点处拍摄的高分辨率图像,确认样品为单晶结构。

概观图像显示了8米长的InSb板,其中种子区域为空。Si籽晶和InSb之间的空隙表明初始成核并非发生在Si表面上,而是在模板内随机发生,与对InAs样品的观察类似。

通过在薄片的几个不同位置拍摄高分辨率图像,进一步显示了InSb样品的单晶性。在制备用于TEM研究的薄片的过程中,还观察到了InSb样品的非晶化或表面改性现象。

这种效应是已知的,并且在用于铟基III-V半导体(InP、InAs)时也存在。即使在进行低能铣削时,仍可观察到一些表面损伤,为了提取晶体信息,对HR-TEM图像进行FFT分析,结果显示晶体的取向为,在样品中没有检测到晶界或位错。

-

细数中芯国际当年被台积电打压的至暗时刻,招招把中芯往绝路上逼

2025-04-15 -

容百科技2023年净利5.81亿同比下滑57.07% 董事长白厚善薪酬421.91万

2025-11-18 -

新奥集团来康生命健康科技王亮一行赴怀仁康养开展产业合作交流

2026-01-06 -

西北农林科技大学被曝开学前给宿舍门刷油漆,学生反映气味刺鼻、头晕 校方回应

2026-01-26