在电磁流量计和生物电测量等应用中,小差分信号与大得多的差分偏移串联。这些偏移通常会限制电路在前端设计中可以获得的增益,进而影响整体动态范围。当使用较低电源电压时,例如在电池供电的信号链中,增益限制更具挑战性。解决这个大差分偏移问题的一种方案是使用交流耦合测量信号链。典型的交流耦合信号链包括一个低增益仪表放大器,其后是一个高通滤波器和额外的增益级(请参阅"放大具有大直流偏移的交流信号以支持低功耗设计")。

低功耗架构没有像其他典型架构(例如由两个或三个运放构成的仪表放大器)那样的钻石图限制利用外部电阻匹配可以实现良好的增益漂移性能不依赖电阻匹配便可实现高CMRR高阻抗基准引脚

设计规格示例

低功耗应用通常使用单电源,电源电压通常在1.8V和3.6V之间。图1所示电路的设计选择取决于输入信号和偏移的幅度范围及频率。表1列出了图1所示电路的示例设计规格。

该电路的设计选择是在AD8237使用低带宽模式的情况下做出的,以便提高增益灵活性和稳定性。

图1.采用间接电流模式架构的交流耦合信号调理电路

表1.图1所示电路的关键设计规格

设计描述

图1所示电路由微功耗、轨到轨仪表放大器AD8237和零输入交越失真运算放大器ADA4505组成。这两个器件均可由最低3.3V电源VDD供电。

此电路可以输出一个电压VOUT,该电压表示输入端的交流信号VSIGNAL在去除直流偏移电压VOFFSET并经放大后的信号。此电路生成的VMID电压用于将ADA4505的正输入和AD8237增益级输出共模设置为中间电源电压。VMID由分压器(R1、R2)生成,并由另一个ADA4505缓冲。AD8237采用超小型封装(MSOP),ADA4505采用紧凑型晶圆级芯片规模封装(WLCSP)。

设计注意事项

1.ADA4505-2(1/2)的正输入VMID将设置VREF(AD8237的基准引脚)的值,从而设置输出VOUT鉴于共模输入电压与输出范围的关系或钻石图,为确保两个供电轨之间的输出摆幅最大,大多数仪表放大器的最优值为中间电源电压(+VDD/2)。设计仿真部分将介绍一种对此有帮助的钻石图工具。

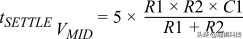

2.考虑电路的总电源电流时,电阻值R1和R2的选择也很重要。电阻选择是噪声与功耗的权衡结果。对于此电路,最好选择较大的电阻值以最大程度地减少额外的电源电流。针对该电阻分压器,增加的额外电源电流将是:

对于电阻分压器(R1、R2),可以增加一个电容C1以对噪声进行限带,并减少对VDD的50Hz/60Hz或其他干扰。电容越大,噪声滤波越好;但是,上电时VMID需要更长的时间才能稳定下来。建立到1%以内所需的时间估计为:

3.选择无源元件值(电阻和电容)时,应考虑容差。对于电阻分压器(R1、R2),目标VMID值可能会移动,这会影响AD8237和ADA4505的输出摆幅范围VOUT。

4.如果应用需要使用高阻抗传感器,可以在AD8237输入端之前使用诸如ADA4505之类的缓冲器,以提供更高输入阻抗和更低输入偏置电流,因为缓冲器会将高阻抗输入转换为低阻抗输出。在整个温度范围内,AD8237的输入偏置电流最大值为1nA。

设计步骤

1.用于设置VMID的分压器:

根据"设计注意事项"的第2点,对于图1中的电路,外围元件的值设置为R1=R2=1MΩ,以使电源电流的贡献保持在1μA左右。

ADA4505之前的电阻分压器的输出:

假设R1和R2的容差为5%,并考虑到ADA4505偏移:

为了消除电阻的交流电源干扰和噪声,设置C1使得截止频率至少小于VSIGNAL最低频率20Hz。请注意,如果需要对噪声进一步限带,电容值可以更大。

在这种情况下,C1设置为22nF,其提供的频率为:

2.仪表放大器(AD8237)增益值VSIGNAL:

考虑电磁流量传感器输出的范围通常是从±75μV到±6mV的峰峰值信号幅度。对于图1所示电路,幅度峰峰值信号幅度范围将设置为VSIGNAL=6mV峰值,频率为30Hz。

然后,考虑AD8237输出摆幅范围对供电轨的限制。这些值可以在数据手册的"输出摆幅"部分中找到。保守起见,我们使用+25°C时RL=10kΩ摆幅情况:

对于3.3V电源:

由于输出是全差分式,因此最差情况下输出相对于VMID的摆幅将是:

对于正输入信号(VMIDMAX=1.732V):

对于负输入信号(VMIDMAX=1.568V):

现在为了设置增益,计算总预期差分输入信号,并使用正负摆幅范围的下限来设置最大摆幅范围:

考虑到输出电压范围限制,AD8237增益应小于253。为了留一些裕量以应对直流误差和其他因素,图1所示电路的增益值应小于最大值。增益和建立时间之间也需要权衡:增益越高,滤波器的时间常数越慢。鉴于以上考量,AD8237增益设置为101。

请注意设计注意事项第1步对摆幅值最大化的好处。

从数据手册可知,增益的相关公式为:

AD8237数据手册提供了不同增益选择的建议电阻值。对于选定的增益101,这些电阻的值应为:RF1=1kΩ,RG1=100kΩ.

3.仪表放大器(AD8237)带宽:

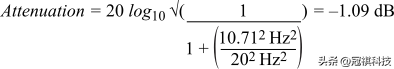

从数据手册得知,截止频率值为

如果设计规格需要对最大信号频率进行某种最低衰减,则对于给定滤波器截止频率,这很容易检查。

4.设置高通滤波器截止频率:

正如"设计注意事项"部分所述,积分器设置的高通滤波器截止频率可能过于接近AD8237带宽设置的低通滤波器截止频率。这会给之前确定的增益带来一些增益错误。

假设R3和C3的容差为±5%,最快时间常数应小于VSIGNAL最低频率:

电阻R3将具有1MΩ的恒定值,以使通过该电阻进入运算放大器的电流最小。

选取最接近的标准电容值,截止频率大致为20Hz,设置C3=1.5μF,故更新后的截止频率为

如果设计规格需要对最小信号频率进行某种最低衰减,则对于给定滤波器截止频率,这很容易检查。请参见此电路的示例:

5.偏移电压:

两个信号VOFFSET和VCM都有限制。

正如预期的那样,直流偏移可能比我们在大多数应用中通常发现的要大。在这种情况下,电压值必须为VOFFSET≤±VMID。如果直流偏移大于此限值,则VREF电压值将超出ADA4505的电源电压范围。与基准引脚相关的公式为:VREF=VMID–VOFFSET。VOFFSET将设置为1V。

至于共模电压,它与VOFFSET值直接相关,因为VCM必须在范围内:

如果未验证这些限制,则AD8237的输入值在电源电压范围以上或以下。VCM将设置为1.65V。

设计仿真

图2.AD8237钻石图工具示例

LTspice®是一款出色的仿真工具,可以检查之前进行的设计过程计算,包括其他有意义的规格,例如目标信号带的噪声性能。LTspice原理图如图3所示。第一个仿真(图4和图5)是瞬态仿真,直流偏移为1V,输入信号为±6mV(30Hz)。图4显示了电路中不同级的信号。图5是图4的放大版本,电路已建立,并且积分器电容充电到最终值。蓝色曲线是AD8237的积分器或基准电压引脚的输出。红色曲线是VMID值(等于VDD/2),绿色曲线是放大的最终30Hz输出信号VOUT。

表2显示了设计目标与瞬态仿真结果的比较。对于最大和最小VOUT值,预期值来自:VOUT=VMID±VSIGNAL×101;就我们的情况而言,预期值等于2.256V和1.044V。VREF预期等于VMID–VOFFSET,就我们的情况而言,预期值为0.65V。VMID等于中间电源电压,就我们的情况而言,它等于1.65V。

表2.设计目标与仿真瞬态分析

图6中的另一个仿真显示了图3中电路的频率响应,直流偏移为1V,输入信号为±6mV(30Hz)。图6中的光标1和2分别放置在高通和低通滤波器的-3dB点。表3显示了设计目标与仿真结果的比较。

表3.设计目标与仿真交流分析

图7中的另一个仿真显示了图3中电路的电压噪声密度与频率RTI的关系。做法是将输出噪声除以解决方案的总增益(101)。对于带通滤波器功能,我们需要选择积分频率区间来计算总噪声。

对于频率上限,我们将使用之前确定的传感器最大频率值,即220Hz。对于频率下限,我们也将使用之前确定的传感器最小频率值,即20Hz。在这种情况下,所产生的噪声将从20Hz积分到220Hz。

由于带通滤波器的截止频率影响,实测噪声实际上会更高。LTspice仿真结果假设其为砖墙滤波器在20Hz和220Hz时急剧滚降。

LTspice中的命令行设置为:.noiseV(VOUT)V1dec10020220。然后按住Ctrl键,鼠标左键单击波形名称(V(ONOISE)/101)。使用下式可轻松将有效值噪声转换为峰峰值噪声:

快速检查AD8237噪声和ADA4505噪声可知,AD8237是主要噪声源。

图3.LTspice原理图

图4.瞬态仿真结果

图5.瞬态仿真结果放大图。

图6.交流仿真结果

图7.在等效噪声带宽上积分的总噪声结果

测量结果

为了验证仿真结果,可以进行硬件测试,因为AD8237和ADA4505都提供了测试板。每个元件的焊接可以根据测试板的原理图完成。同时使用两个测试板时,可能需要切断AD8237板上的走线,以将VMID电压连接到RG电阻。

为了确保更好地理解结果,元件值来自设计步骤部分,与设计仿真相同。为了模拟电磁流量计或生物电测量传感器,我们使用了不同的测量设备,例如电压校准器和任意波形发生器。

对于此测试,输入信号设置为具有1V的直流偏移VOFFSET,共模电压为1.65V,输入信号VSIGNAL为±6mV(30Hz)

查看图8所示的结果,输出电压VOUT黄色曲线)的性能相对于预期值有一个很小的电压差,但仍与预期保持一致。

表4总结了设计目标与测量结果。

表4.设计目标与测量结果

设计目标与仿真结果的差异可能有多种原因。

所使用的电阻具有5%的容差,这意味着VMID值可能有所偏移。试验台设置可能有局限性,导致出现微小偏差,如实测仿真结果VOFFSET和VSIGNAL所示。

图8.示波器屏幕截图,黄色曲线对应于VOUT,蓝色曲线对应于VREF。

设计器件

表5.仪表放大器

表6.运算放大器

结论

-

「司法拍卖」司法拍卖竟然还卖这些东西,想不到吧!

2025-05-31 -

安洁科技取得模具延时脱料机构专利,提高了产品的品质

2025-11-02 -

琦品股份拟分别投资50万设立浦江琦贸科技、浦江琦晖科技、浦江琦酷科技、浦江琦塑科技4家全资子公司

2025-07-10 -

国企招聘 | 上海电气新能源科技发展有限公司发布招聘

2025-10-18